A.P. Papliński

#### **Combinational circuits** 6

# 6.1 Introductory concepts

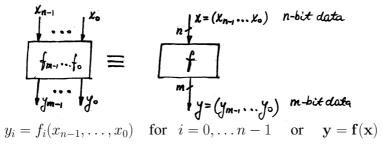

• A combinational circuit (block, component) consists of logic gates and processes n input signals  $x(n-1), \ldots, x(0)$  into m output signals  $y(m-1), \ldots, y(0)$  using a function y = f(x), in such a way that output signals depend only on the **current** input signals.

where each  $f_i$  is a logic function.

- Past values of the input signals do not have any influence on the current values of the output signals.

- Description of any combinational circuit with n inputs and m outputs can be ultimately reduced to a truth table with  $2^n$  rows and m column.

- From the point of view of their internal structures combinational blocks can be classified into two groups:

- un-structured circuits, that is a "random" collection of gates,

- structured circuits forming 1-D and 2-D arrays of components.

A.P. Papliński

Digital Logic/Design. - L. 6

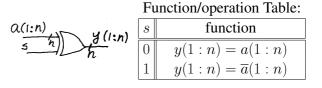

- The simplest combinational blocks are collections of gates. For example, an n-bit NAND gate:

- A slightly more complicated example includes the collection of gates driven by a common control signal, say s, to perform two operations:

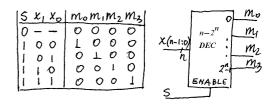

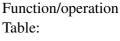

- We are already familiar with a n-to- $2^n$  decoder as a minterm/maxterm generator. Typically the decoder has an additional enable signal s such that the minterms are generated only for s=1, whereas for s=0 outputs are in an inactive state, typically 0.

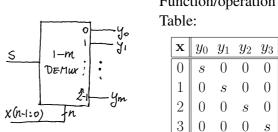

- The decoder can be also used as a **Demultiplexer**. The 1-bit demultiplexer receives 1-bit data on a single input and re-directs it into one-out-of  $m = 2^n - 1$  outputs selected by an n-bit number x

$$\frac{a(1:n)}{b(1:n)} \qquad \qquad y=\overline{a\cdot b}$$

March 22, 2006

6-1

### 6.2 Example of a VHDL code for a 2-to-4 decoder

```

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.std_logic_arith.all;

ENTITY dec2to4 IS

PORT (

x : IN

std_logic_vector (1 DOWNTO 0);

y : OUT

std_logic_vector (3 DOWNTO 0)

);

END dec2to4 ;

ARCHITECTURE struct OF dec2to4 IS

SIGNAL xb : std_logic_vector(1 DOWNTO 0);

BEGIN

y(0) \le xb(1) \text{ AND } xb(0);

y(1) \le xb(1) AND x(0);

y(2) \le xb(0) AND x(1);

y(3) \le x(1) AND x(0);

xb <= NOT(x);

END struct;

```

- A VHDL program represents a digital circuit.

- It can represent: signal flow, behaviour or structure of the circuit

- The program can be used to simulation/test, or to synthesize the digital circuit

- The above program describes signal flow

- All assignment statements are interpreted/executed **concurrently**, therefore can be written in **any order**.

A.P. Papliński

Digital Logic/Design. - L. 6

### 6.3 Multiplexers

- A **n-to-1 multiplexer** connects its output y to one of  $n = 2^m$  inputs  $a_0, a_1, \ldots a_n$  selected by an m-bit control/select signal s.

- In other words the multiplexer output is a sum of products of input signals with respective minterms:

$$y = a_0 \cdot m_0 + a_1 \cdot m_1 + \ldots + a_{n-1} \cdot m_{n-1} = \sum_{i=0}^{n-1} a_i \cdot m_i$$

ao

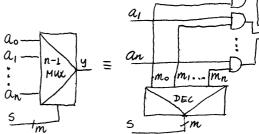

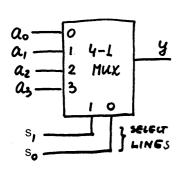

• A 4-to-1 multiplexer can be implemented in the following way:

Function Table:

6–3

March 22, 2006

s

0

1

2

3

v

$y \ll 0$

a(0)

a(1)

a(2)

a(3)

6 - 5

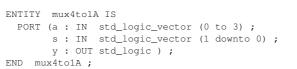

#### 6.4 Describing a multiplexer in VHDL

There are a number of ways to describe a multiplexer in VHDL. The following two methods use various concurrent assignment statements. We use a 4-to-1 multiplexer as an example.

### 6.4.1 Conditional Signal Assignment Statement

#### <= ... when ... else

#### 6.4.2 Selected Signal Assignment Statement

<= with ... select ... when ..., ...;

a(0:3)

s(1:0)

a(0)

a(1)

a(2)

a(3) 3 1 0

n

1 MUX

2 4to1

'o

```

ARCHITECTURE selSA OF mux4tolA IS

BEGIN

WITH s SELECT

y <= a(0) WHEN "00" , -- comma

a(1) WHEN "01" ,

a(2) WHEN "10" ,

a(3) WHEN OTHERS ; -- semicolon

END selSA ;

```

A.P. Papliński

```

Digital Logic/Design. — L. 6 March 22, 2006

```

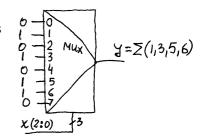

Multiplexer as a universal logic element

- Typically multiplexers are used to re-direct signals from different sources onto a common output.

- However, when we compare expression for canonical implementation of a logic function with expression for a multiplexer we note that they are structurally identical.

- It means that a multiplexer with *m* select signals can be used as a universal logic block implementing any logic function of *m* variables specified by constants (from a truth table) at the multiplexer inputs.

- As an example consider implementation of a 3-variable function using an 8-to-1 multiplexer:

$$y = f(x_2, x_1, x_0) = \sum (1, 3, 5, 6)$$

- If we allow inputs to the multiplexer to be not only constants (0, 1), but also variable(s) (or their complements), then, in particular, using a  $2^m$ -to-1 multiplexer, we can implement any logic function of m + 1 variables.

- In such a case m variables are applied to the select inputs of the multiplexer, whereas the remaining variable, its complement and constants (0, 1) are applied to the multiplexed inputs.

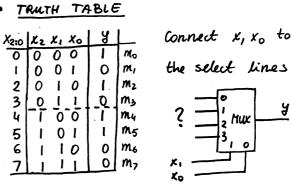

# Example

Implement a 3-variable function

$$y = f(x_2, x_1, x_0) = \sum (1, 3, 4, 5)$$

using a 2<sup>2</sup>-to-1 multiplexer

- Variables  $(x_1, x_0)$  are used as the select variables in a 4-to-1 multiplexer

- The remaining variable  $x_2$  will be used at the multiplexer inputs.

- To do this we modify the truth table comparing values of the output signal *y* for two values of the variable *x*<sub>2</sub>

· MODIFIED TRUTH TABLE X, Xo m'. 0 Я MUX 1 m' 0 1 X2 m2  $\overline{X_2}$ 2 ×ء 2 L 0 0 m2 3 I 0 T Ο  $y = m_0 + m_2 + m_4 + m_5$  $= m_0 \cdot 1 + m_1 \cdot x_2 + m_2 \cdot \overline{x_2} + m_3 \cdot 0$

Digital Logic/Design. - L. 6

# 6.5 Unstructured combinational circuits

- The name "unstructured" refers to implementations of a *n*-input *m*-output combinational circuit build from simple gates which are not grouped into any sub-blocks.

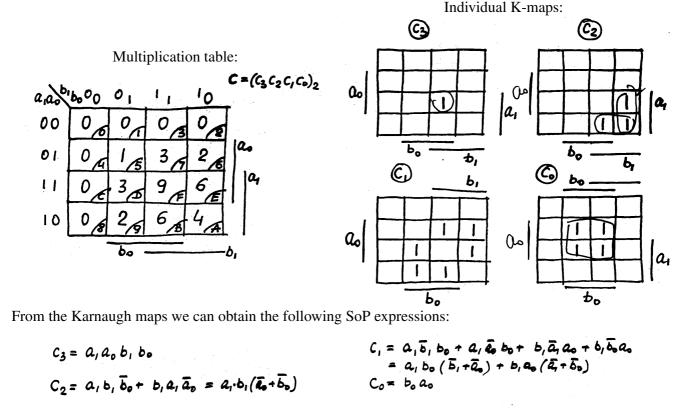

- To illustrate the concept let us consider the following implementation of a 2-bit multiplier.

- It is a 2-bit by 2-bit multiplication circuit that forms a 4-bit product:

| a b<br>a $ba$ $b$                                                                                                  | $a = (a_1 a_0)_2$ is a 2-bit muthurand                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X                                                                                                                  | b=(b, bo)2 is a 2-bit multiplier                                                                                                                                                                                              |

| <u> </u>                                                                                                           | $C = (C_3 C_2 C_1 C_0)_2$ is a 4-bit product                                                                                                                                                                                  |

| te                                                                                                                 | such that $[C = a \times b] = f(a, b)$                                                                                                                                                                                        |

| $\begin{array}{c} a_{1} a_{0}  b_{1}  b_{0} \\ \hline \\ \hline \\ \\ \hline \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $ | 4 Boolean functions of<br>4 variables must be derived<br>$C_3 = f_3(a_{ij}a_{0j}b_{ij}b_{0})$<br>$C_2 = f_2(a_{ij}a_{0j}b_{ij}b_{0})$<br>$C_5 = f_1(a_{ij}a_{0j}, b_{ij}, b_{0})$<br>$C_0 = f_0(a_{ij}a_{0j}, b_{ij}, b_{0})$ |

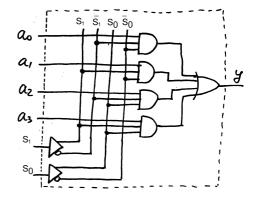

| F | unc  | TION   | TAB   | ιe | TR    | MTH        | TA         | BLÊ                                                                        |

|---|------|--------|-------|----|-------|------------|------------|----------------------------------------------------------------------------|

|   | a    | Ь      | C     | Γſ | a, a0 | 6,60       | m          | C3 C2 C1 C0                                                                |

|   | 0000 | 0-230- | -0000 |    | ND    | 0-0-0-0-0- | 0-00-0     | 0 0 0 0<br>0 0 0 0<br>0 0 0 0<br>0 0 0<br>0 0 0<br>0 0 0<br>0 0 0<br>0 0 0 |

|   |      | 23     | -23   |    | VI    | İ          | 67         | 0010                                                                       |

|   | ~~~~ | 0-97   | 0240  |    |       |            | - 0 - C PA | 0 0 00                                                                     |

6 - 7

March 22, 2006

The next step is to convert the truth table into the Karnaugh maps:

A.P. Papliński

Digital Logic/Design. — L. 6

# March 22, 2006

6–9

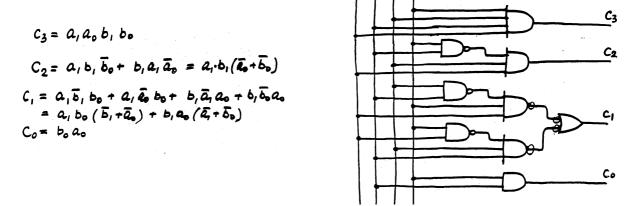

# A possible implementation with "mixed" gates: AND, OR NAND

Note that equation for  $c_1$  has been simplified so that it is no longer a standard form but a 3-level implementation:

a, ao b, b.

The above implementation is an example of an unstructured combinational circuit.